**Instruction Manual**

# Tektronix

TMSPGC PGA370 Single-Ended/Differential Clock Hardware Support

071-0803-01

Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software – Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Tektronix, Inc., P.O. Box 500, Beaverton, OR 97077

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that the media on which this software product is furnished and the encoding of the programs on the media will be free from defects in materials and workmanship for a period of three (3) months from the date of shipment. If a medium or encoding proves defective during the warranty period, Tektronix will provide a replacement in exchange for the defective medium. Except as to the media on which this software product is furnished, this software product is provided "as is" without warranty of any kind, either express or implied. Tektronix does not warrant that the functions contained in this software product will meet Customer's requirements or that the operation of the programs will be uninterrupted or error-free.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period. If Tektronix is unable to provide a replacement that is free from defects in materials and workmanship within a reasonable time thereafter, Customer may terminate the license for this software product and return this software product and any associated materials for credit or refund.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPLACE DEFECTIVE MEDIA OR REFUND CUSTOMER'S PAYMENT IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

## **Table of Contents**

|                              | General Safety Summary                                          | v             |

|------------------------------|-----------------------------------------------------------------|---------------|

|                              | Service Safety Summary                                          | vii           |

|                              | Preface         Manual Conventions         Contacting Tektronix | ix<br>ix<br>x |

| Getting Started              |                                                                 |               |

|                              | Getting Started                                                 | 1-1           |

|                              | Support Package Description                                     | 1-1           |

|                              | Support Software Compatibility                                  | 1-1           |

|                              | Logic Analyzer Configuration                                    | 1-1           |

|                              | Requirements and Restrictions                                   | 1-2           |

|                              | Labeling P6434 Probes                                           | 1-2           |

|                              | Assembling the Probe Adapter                                    | 1-4           |

|                              | Connecting the Logic Analyzer to a Target System                | 1-6           |

|                              | Configuring the Probe Adapter                                   | 1-11          |

|                              | MODE Jumper                                                     | 1-11          |

|                              | FREQUENCY Jumper                                                | 1-11          |

|                              | Alternate Connections          Applying and Removing Power      | 1-12<br>1-14  |

| Reference                    |                                                                 |               |

|                              | Reference: Channel Tables                                       | 2-1           |

|                              | Channel Assignments                                             | 2-1           |

| Specifications               |                                                                 |               |

|                              | Specifications                                                  | 3-1           |

|                              | Circuit Description                                             | 3-1           |

|                              | Probe Adapter Loading Diagrams                                  | 3-2           |

|                              | Specification Tables                                            | 3-4           |

| Maintenance                  |                                                                 |               |

|                              | Maintenance                                                     | 4-1           |

|                              | Replacing The Fuse                                              | 4-1           |

| <b>Replaceable Parts Lis</b> | st                                                              |               |

|                              | Replaceable Parts List                                          | 5-1           |

|                              | Parts Ordering Information                                      | 5-1           |

|                              | Using the Replaceable Parts List                                | 5-1           |

| Index                        |                                                                 |               |

# **List of Figures**

| Figure 1-1: Seating the 190-pin Mictor connector                        | 1-4  |

|-------------------------------------------------------------------------|------|

| Figure 1-2: Attaching the Logic board to the Interposer board           | 1-5  |

| Figure 1-3: TMSPGC probe adapter protective sockets                     | 1-7  |

| Figure 1-4: Inserting a protective socket into the ZIF socket           | 1-7  |

| Figure 1-5: Inserting the probe adapter into the socket                 | 1-8  |

| Figure 1-6: Placing the PGA370 microprocessor into the probe adapte 1-9 | er   |

| Figure 1-7: Connecting a probe to the probe adapter                     | 1-10 |

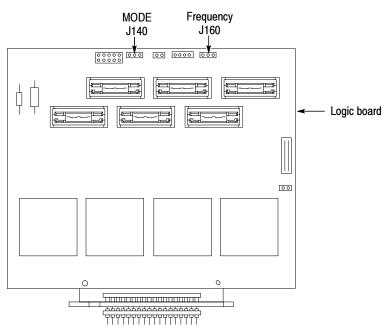

| Figure 1-8: Jumper locations on the TMSPGC probe adapter                | 1-11 |

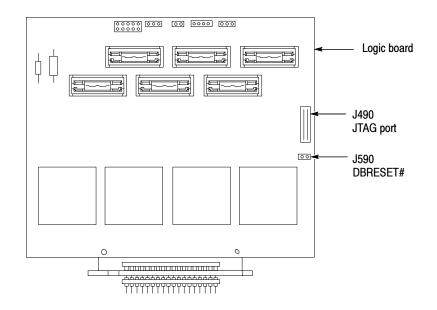

| Figure 1-9: JTAG port locations on the probe adapter                    | 1-13 |

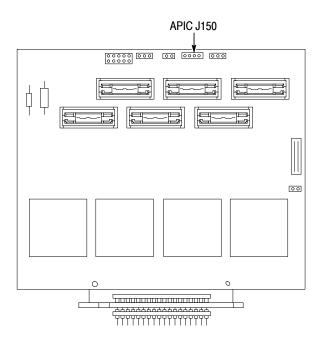

| Figure 1-10: APIC pin locations on the probe adapter                    | 1-14 |

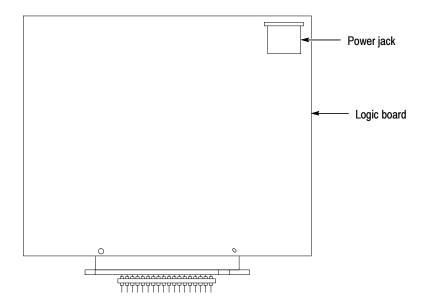

| Figure 1-11: Location of the power jack                                 | 1-15 |

| Figure 3-1: BCLK and BCLK# signals with active loads                    | 3-2  |

| Figure 3-2: AGTL signals with active loads, except RESET#               | 3-2  |

| Figure 3-3: CMOS signals with active loads, plus RESET#                 | 3-3  |

| Figure 3-4: JTAG signals without active loads                           | 3-3  |

| Figure 3-5: Equivalent circuit for the P6434 probe                      | 3-4  |

| Figure 3-6: Dimensions of the TMSPGC probe adapter                      | 3-8  |

| Figure 4-1: Fuse location on the TMSPGC probe adapter                   | 4-1  |

| Figure 5-1: Exploded view of the TMSPGC PGA370 probe adapter            | 5-6  |

## **List of Tables**

| Table 1-1: DBRESET information                             | 1-12 |

|------------------------------------------------------------|------|

| Table 1-2: APIC information                                | 1-13 |

|                                                            | 0.1  |

| Table 2-1: Clock channels assignments                      | 2-1  |

| Table 2-2: Qualifier channel assignments                   | 2-1  |

| Table 2-3: Master A channel assignments                    | 2-2  |

| Table 2-4: Master D channel assignments                    | 2-3  |

| Table 2-5: Master C channel assignments                    | 2-4  |

| Table 2-6: Slave A channel assignments                     | 2-5  |

| Table 2-7: Slave D channel assignments                     | 2-7  |

| Table 2-8: Slave C channel assignments                     | 2-8  |

| Table 3-1: Lossy delay line values                         | 3-4  |

| Table 3-2: Electrical specifications for the target system | 3-5  |

| Table 3-3: BCLK and BCLK# electrical specifications,       |      |

| differential clock                                         | 3-5  |

| Table 3-4: BCLK and CLKREF electrical specifications,      |      |

| single-ended clock                                         | 3-5  |

| Table 3-5: AGTL electrical specifications                  | 3-6  |

| Table 3-6: CMOS electrical specifications (1.5 V)          | 3-6  |

| Table 3-7: Electrical specifications for the AC adapter    | 3-6  |

| Table 3-8: Environmental specifications                    | 3-7  |

|                                                            |      |

Table of Contents

# **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it. To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the *General Safety Summary* in other system manuals for warnings and cautions related to operating the system.

| To Avoid Fire or | <b>Use Proper Power Cord.</b> Use only the power cord specified for this product and |

|------------------|--------------------------------------------------------------------------------------|

| Personal Injury  | certified for the country of use.                                                    |

**Connect and Disconnect Properly.** Connect the probe output to the measurement instrument before connecting the probe to the circuit under test. Disconnect the probe input and the probe ground from the circuit under test before disconnecting the probe from the measurement instrument.

**Observe All Terminal Ratings.** To avoid fire or shock hazard, observe all ratings and markings on the product. Consult the product manual for further ratings information before making connections to the product.

Do not apply a potential to any terminal, including the common terminal, that exceeds the maximum rating of that terminal.

Use Proper AC Adapter. Use only the AC adapter specified for this product.

**Do Not Operate Without Covers.** Do not operate this product with covers or panels removed.

Use Proper Fuse. Use only the fuse type and rating specified for this product.

**Avoid Exposed Circuitry.** Do not touch exposed connections and components when power is present.

**Do Not Operate With Suspected Failures.** If you suspect there is damage to this product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

Keep Product Surfaces Clean and Dry.

**Provide Proper Ventilation.** Refer to the manual's installation instructions for details on installing the product so it has proper ventilation.

#### **Symbols and Terms**

Terms in this Manual. These terms may appear in this manual:

**CAUTION.** Caution statements identify conditions or practices that could result in damage to this product or other property.

Terms on the Product. These terms may appear on the product:

CAUTION indicates a hazard to property including the product.

Symbols on the Product. The following symbols may appear on the product:

Double Insulated Protective Ground (Earth) Terminal

# **Service Safety Summary**

Only qualified personnel should perform service procedures. Read this *Service Safety Summary* and the *General Safety Summary* before performing any service procedures.

**Do Not Service Alone.** Do not perform internal service or adjustments of this product unless another person capable of rendering first aid and resuscitation is present.

**Disconnect Power.** To avoid electric shock, switch off the instrument power, then disconnect the power cord from the mains power.

**Use Care When Servicing With Power On.** Dangerous voltages or currents may exist in this product. Disconnect power, remove battery (if applicable), and disconnect test leads before removing protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

## **Preface**

This instruction manual contains specific information about the TMSPGC PGA370 microprocessor support package and is part of a set of information on how to operate this product on compatible Tektronix logic analyzers.

If you are familiar with operating microprocessor support packages on the logic analyzer for which the TMSPGC PGA370 support was purchased, you will only need this instruction manual to set up and run the support.

If you are not familiar with operating microprocessor support packages, you will need to supplement this instruction manual with *TMS 115 IA32G5 Software Support* manual and information on basic operations in your online help to set up and run the support.

This manual provides detailed information on the following topics:

- Assembling and configuring the probe adapter

- Connecting the logic analyzer to the system under test

- Applying power and operating the probe adapter

#### **Manual Conventions**

This manual uses the following conventions:

- The phrase "information on basic operations" refers to basic information in your Tektronix logic analyzer online help.

- The term Master module refers to the module in the lower-numbered slot and the term Slave module refers to the module in the higher-numbered slot.

The portable logic analyzer has the lower numbered slots on the top and the benchtop logic analyzer has the lower numbered slots on the left.

## **Contacting Tektronix**

| Phone             | 1-800-833-9200*                                                                                                             |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Address           | Tektronix, Inc.<br>Department or name (if known)<br>14200 SW Karl Braun Drive<br>P.O. Box 500<br>Beaverton, OR 97077<br>USA |

| Web site          | www.tektronix.com                                                                                                           |

| Sales support     | 1-800-833-9200, select option 1*                                                                                            |

| Service support   | 1-800-833-9200, select option 2*                                                                                            |

| Technical support | Email: techsupport@tektronix.com<br>1-800-833-9200, select option 3*<br>6:00 a.m 5:00 p.m. Pacific time                     |

\* This phone number is toll free in North America. After office hours, please leave a voice mail message.

Outside North America, contact a Tektronix sales office or distributor; see the Tektronix web site for a list of offices.

# **Getting Started**

## **Getting Started**

This section contains information on the TMSPGC PGA370 hardware support package and connecting the logic analyzer to the target system.

#### **Support Package Description**

The TMSPGC probe adapter is nonintrusive hardware that allows the logic analyzer to acquire data from a microprocessor in its own operating environment with little affect on that system.

The TMSPGC probe adapter is an interposer design. The probe adapter connects to the target system, and then, the microprocessor connects to the probe adapter. Signals from the microprocessor-based system flow through the probe adapter into the P6434 probes and through the probe cables to the logic analyzer.

#### Support Software Compatibility

The TMSPGC probe adapter requires a Tektronix microprocessor software support package. This TMSPGC probe adapter is used with the TMS 115 Software Support package.

#### Logic Analyzer Configuration

To use the TMSPGC PGA370 hardware support package you need a Tektronix logic analyzer equipped with two 102-channel modules. The modules must be in adjacent slots and merged.

References to a 204-channel module include the two 102-channel modules that are merged and any other merged module combination of a minimum of 204-channels (for the merged combination).

You can acquire JTAG and APIC bus activity through the TMSPGC probe adapter. Probing the APIC bus requires the TMS 801 APIC bus support package, a third 102-channel acquisition module, and standard probes. See *Alternate Connections* on page 1–12 for more details.

### **Requirements and Restrictions**

**CAUTION.** Forced air cooling must be used to keep the microprocessor from overheating.

You should review the general requirements and restrictions of microprocessor support packages in the information on basic operations as they pertain to the target system.

You should also review electrical, environmental, and mechanical specifications in *Specifications* on page 3-1 as they pertain to the target system, as well as the following descriptions of other TMSPGC PGA370 hardware support requirements and restrictions.

**System Clock Rate** The TMSPGC PGA370 microprocessor support can acquire data from the PGA370 microprocessors operating at speeds of up to 133 MHz.

The operating clock rate specifications were measured at the time of printing. Contact your Tektronix sales representative for current information on the fastest devices supported.

- **BCLK** The TMSPGC PGA370 hardware support can operate with either a low-voltage differential clock, or with a normal voltage single-ended clock. Refer to the BCLK specifications listed in Table 3-3 and 3-4 beginning on page 3-5, in the *Specifications* chapter.

- **AGTL** The TMSPGC PGA370 hardware support can operate with either AGTL (1.2 volt) or AGTLT (1.5 volt) logic levels. Refer to the AGTL specifications listed in Table 3-5 on page 3-6.

- **CMOS** The TMSPGC PGA370 hardware support can operate with only 1.5 volt CMOS logic levels. Refer to the CMOS specifications listed in Table on page .

- Target System PowerWhenever you power off the target system, remove power from the probe<br/>adapter. Refer to Applying and Removing Power on page 1–14.

#### Labeling P6434 Probes

The TMSPGC PGA370 hardware support package relies on the standard channel mapping and labeling scheme for P6434 probes. Apply labels using the standard method described in the *P6434 Mass Termination Probe Instructions*.

#### **Signals Acquired**

The following signals are acquired by the TMSPGC probe adapter:

| A20M#      | BINIT#    | DEP[7:0]# | IERR#     | PWRGOOD  | STPCLK#  |

|------------|-----------|-----------|-----------|----------|----------|

| A[35:3]    | BNR#      | DEFER#    | IGNNE#    | RESET#   | THRMTRP# |

| ADS#       | BP[3:2]#  | DID[7:0]# | INIT#     | REQ[4:0] | ТСК      |

| AERR#      | BPM[1:0]# | DRDY#     | LOCK#     | RP#      | TDI      |

| ATTR[7:0]# | BPRI#     | EXF[4:0]# | LINT[1:0] | RSP#     | TDO      |

| AP[1:0]#   | BREQ0#    | FLUSH#    | PICD[1:0] | RS[2:0]# | TMS      |

| BE[7:0]#   | D[63:0]   | FERR#     | PICCLK    | SLP#     | TRST#    |

| BERR#      | DBSY#     | HIT#      | PRDY#     | SMI#     | TRDY#    |

| BCLK       |           | HITM#     | PREQ#     |          |          |

**Signals Not Acquired** The following signals are not acquired by the TMSPGC probe adapter:

| PGA370 signal name | PGA370 pin number |

|--------------------|-------------------|

| BSEL[0]            | AJ33              |

| BSEL[1]            | AJ31              |

| CPUPRES#           | C37               |

| NCHCTRL            | N37               |

| PLL1               | W33               |

| PLL2               | U33               |

| RTTCTRL            | S35               |

| SLEWCTRL           | E27               |

| THRMDN             | AL29              |

| THRMDP             | AL31              |

| VID25mv            | AK36              |

| VID[0]             | AL35              |

| VID[1]             | AM36              |

| VID[2]             | AL37              |

| VID[3]             | AJ37              |

| VTT_PWRGD          | AK4               |

## Assembling the Probe Adapter

The probe adapter assembly consists of a Logic board, Interposer board, three protective sockets (disassembly, timing analysis, and JTAG debugging), and screws.

**CAUTION.** To prevent static discharge from damaging the microprocessor, the probe adapter, the probes, and the module, handle components only in a static-free environment.

Always wear a grounding wrist strap, heel strap, or similar device while handling the microprocessor and probe adapter.

Do the following steps to assemble the probe adapter:

- 1. To discharge any static electricity, touch the ground connector located on the logic analyzer. Then, before you remove the probe adapter circuit boards from their protective bags, touch each bag to discharge stored static electricity.

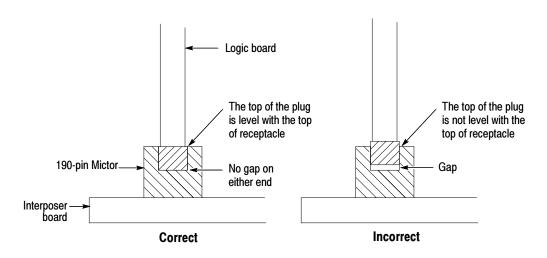

- 2. Align the Logic board connector pins with the Interposer board connector pins, and press firmly to seat the board connector (see Figure 1-1). Both connectors are polarized and only mate in one orientation.

**NOTE**. To ensure a reliable electrical connection between the Logic board and the Interposer board the 190-pin Mictor connector must be completely seated at both ends (see Figure 1-1).

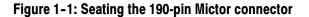

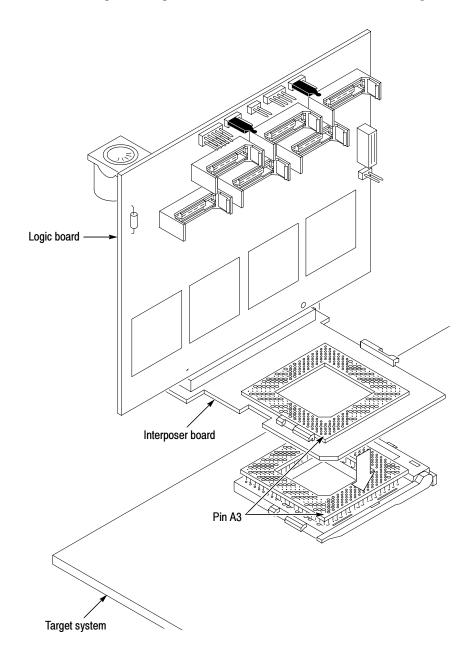

**3.** Align the mounting brackets on the logic board with the mounting holes on the interposer board, and attach with the provided screws (see Figure 1-2).

**CAUTION.** To prevent damage to the probe adapter, use the provided screws to secure the logic board to the Interposer board.

Figure 1-2: Attaching the Logic board to the Interposer board

## Connecting the Logic Analyzer to a Target System

Your target system must allow clearance for the probe adapter. Refer to the dimensions on page 3-8 for the required clearances.

To connect the logic analyzer to the target system, follow these steps:

1. Power off the target system. It is not necessary to power off the logic analyzer.

**CAUTION.** To prevent static discharge from damaging the microprocessor, the probe adapter, the probes, and the acquisition module, handle the components only in a static-free environment.

Always wear a grounding wrist strap, heel strap, or similar device while handling the microprocessor and probe adapter.

2. Follow the procedure from the microprocessor vendor to remove the microprocessor from the PGA370 socket on the target system.

**NOTE**. Do not remove the protective socket from the bottom of the probe adapter. Do not install a protective socket without removing all existing sockets from the target system.

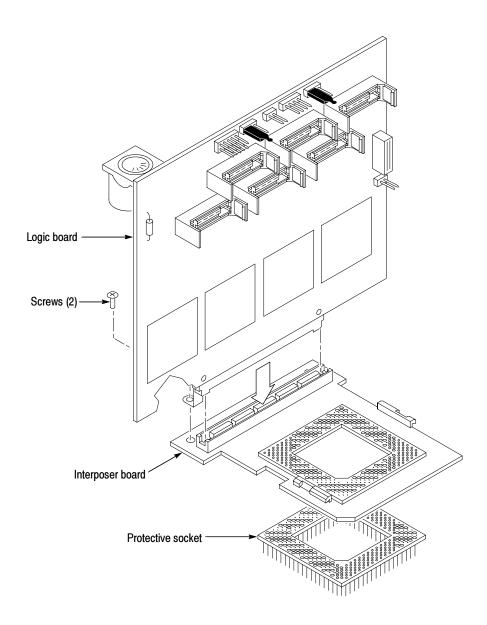

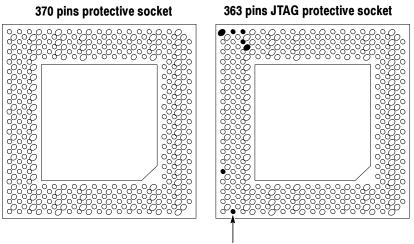

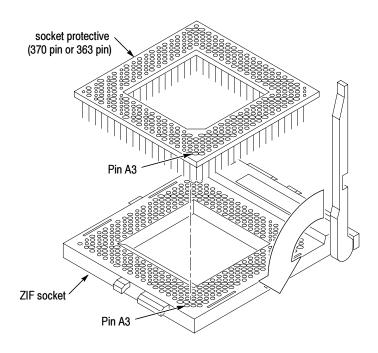

**3.** Choose the correct protective socket (see Figure 1-3).

When using the TMSPGC probe adapter:

- Use the 363-pin protective socket only when using the JTAG port on the TMSPGC probe adapter.

- Use the 370-pin protective socket at all other times.

Black holes are missing pins

#### Figure 1-3: TMSPGC probe adapter protective sockets

- **4.** Align the A3 pin indicator on the protective socket with pin A3 of the PGA370 protective socket on the target system.

- 5. Insert the protective socket into the target system as shown in Figure 1-4.

Figure 1-4: Inserting a protective socket into the ZIF socket

- 6. Align the A3 pin indicator on the probe adapter with the A3 pin indicator on the installed socket.

- 7. Insert the probe adapter into the installed socket as shown in Figure 1-5.

Figure 1-5: Inserting the probe adapter into the socket

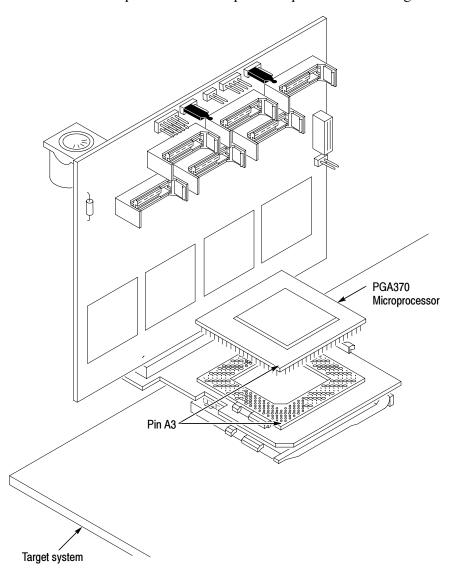

8. Insert the microprocessor into the probe adapter as shown in Figure 1-6.

Figure 1-6: Placing the PGA370 microprocessor into the probe adapter

9. Reattach the heat sink from the target system to the probe adapter.

Attach the P6434 probesAfter you have connected the probe adapter to the target system, connect three<br/>P6434 probes to the Master module and three P6434 probes to the Slave module.<br/>The module in the lower-numbered slot is referred to as the Master module and<br/>the module in the higher-numbered slot is referred to as the Slave module.

The portable logic analyzer has the lower numbered slots on the top and the benchtop logic analyzer has the lower numbered slots on the left.

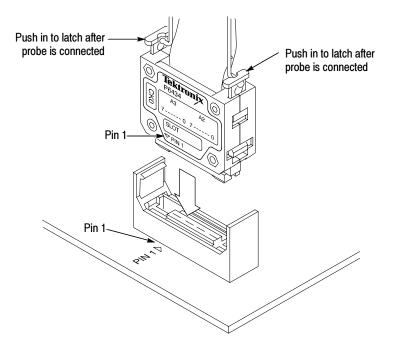

1. Match the A, C, and D probes from the Master module with the corresponding M\_A, M\_C, and M\_D probe connectors on the probe adapter. Align the pin 1 indicator on the probe label with the pin 1 indicator of the connector on the probe adapter.

**CAUTION.** Incorrect handling of the P6434 probe while connecting it to the probe adapter can result in damage to the probe or to the mating connector on the probe adapter. To avoid damaging the probe and probe adapter, always position the probe perpendicular to the mating connector and gently connect the probe.

- 2. Position the probe tip perpendicular to the mating connector and gently connect the probe (see Figure 1-7).

- 3. When connected, push latch releases in to set the latch on the probe .

#### Figure 1-7: Connecting a probe to the probe adapter

- 4. Match the A, C, and D probes from the Slave module with the corresponding S\_A, S\_C, and S\_D probe connectors on the probe adapter. Align the pin 1 indicator on the probe label with pin 1 of the connector on the probe adapter.

- 5. Repeat steps 2 and 3.

## **Configuring the Probe Adapter**

The probe adapter uses jumpers to acquire data for disassembly or for timing analysis. Figure 1-8 shows the location of the jumpers.

**MODE Jumper** Place the MODE select jumper, J140, in the NORMAL position to acquire data for disassembly (IA32G5) or synchronous timing analysis (IA32G5\_T) using Custom clocking.

Place the MODE select jumper, J140, in the TRANSPARENT position to acquire data for asynchronous timing analysis with the IA32G5\_T setup using Internal clocking.

**NOTE**. Due to setup/hold requirements, the TRANSPARENT mode is not recommended for synchronous acquisitions. All synchronous timing analysis is done in the NORMAL mode with the IA32G5\_T setup.

**FREQUENCY Jumper** Place the FREQUENCY select jumper J160, in the HI position when operating between 120 and 200 MHz. Place the FREQUENCY select jumper J160, in the LO position when operating between 60 and 140 MHz.

Figure 1-8 shows the location of J140 and J160 on the probe adapter.

Figure 1-8: Jumper locations on the TMSPGC probe adapter

## **Alternate Connections**

JTAG The TMSPGC probe adapter logic board provides J490 as a way to connect to JTAG debugging hardware. JTAG debugging hardware is not included with the TMSPGC PGA370 hardware support package. Contact your microprocessor vendor for information on how to obtain JTAG debugging hardware.

**NOTE**. The JTAG circuitry on the Logic board is active only when the JTAG device is connected to J490. If the JTAG device is disconnected from J490, all JTAG data and control lines on the logic board are tristated.

**Optional System Reset.** The JTAG circuitry on the Logic board does not allow external JTAG debugging hardware to induce a system reset through the DBRESET# signal on the JTAG port. If you need to use this feature you must provide the connection from these pins to the target system. The following Table 1-1 lists the signals on the J590.

#### Table 1-1: DBRESET information

| J590 Pin number | JTAG signal name |

|-----------------|------------------|

| 1               | GND              |

| 2               | DBRESET#         |

Figure 1-9 shows the location of the DBRESET# and JTAG port on the logic board of the probe adapter.

When using the JTAG port on the TMSPGC probe adapter, use the 363 pin protective socket (see page 1-6). Use the 370 pin protective socket at all other times.

#### Figure 1-9: JTAG port locations on the probe adapter

**APIC** Four pins on J150 are provided to connect the TMS801 APIC bus probe adapter to the PICCLK, PICD0, and PICD1 signals for APIC bus support. The TMS801 APIC bus probe adapter is not included with the TMSPGC hardware support package. Contact a Tektronix representative for information on how to obtain the TMS801 APIC bus probe adapter.

| J150 Pin number | Microprocessor<br>pin name | Microprocessor signal name |

|-----------------|----------------------------|----------------------------|

| 1               | GND                        | -                          |

| 2               | J33                        | PICCLK                     |

| 3               | L35                        | PICD1                      |

| 4               | J35                        | PICD0                      |

| Table 1-2: APIC information | Table | 1-2:/ | APIC | information |

|-----------------------------|-------|-------|------|-------------|

|-----------------------------|-------|-------|------|-------------|

Figure 1-10 show the APIC bus signal pins for the TMSPGC probe adapter.

Figure 1-10: APIC pin locations on the probe adapter

#### **Applying and Removing Power**

An AC adapter for the TMSPGC probe adapter is included with this TMSPGC PGA370 hardware support. The AC adapter provides +5 volt power to the probe adapter.

**NOTE**. Whenever you power off the target system, be sure to remove power from the probe adapter.

To apply power to the TMSPGC probe adapter and target system, follow these steps:

**CAUTION.** Failure to use the +5 VAC adapter provided by Tektronix can permanently damage the probe adapter, PGA370 microprocessor, and target system. Do not mistake another AC adapter that looks similar to the +5 VAC adapter.

1. Connect the +5 V AC adapter to the jack on the probe adapter. Figure 1-11 shows the location of the jack on the Logic board.

**NOTE**. Failure to apply power to the probe adapter before applying power to the target system may cause erratic behavior.

- 2. Plug the AC adapter for the probe adapter into an electrical outlet. When power is present on the probe adapter, an LED lights near the power jack. Also, four green LEDs are lighted on the front side of the Logic board.

- **3.** Power on the target system.

Figure 1-11: Location of the power jack

To remove power from the target system and the probe adapter, follow these steps:

**NOTE**. Failure to power down the target system before removing power from the probe adapter may cause erratic behavior.

- 1. Power off the target system.

- 2. Unplug the AC adapter for the probe adapter from the electrical outlet.

Getting Started

# Reference

## **Reference: Channel Tables**

This section lists the channel group tables for disassembly and timing.

#### **Channel Assignments**

Channel assignments shown in Tables 2–1 through 2–8 use the following conventions:

- All signals where a CPU pin number is not listed are derived signals.

- A pound sign (#) following a signal name indicates an active low signal.

- The CPU pin number always applies to the IA32G5\_T column and to the IA32G5 column, except those signals that are indicated as demuxed during the B phase of a request.

Tables 2-1 and 2-8 list the logic analyzer channel assignments.

| Clock<br>channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin numbers |

|------------------|--------------------------------|----------------------------------|--------------------|

| M_CLK:3          |                                |                                  |                    |

| M_CLK:2          |                                | TDO                              | AN37               |

| M_CLK:1          | PHASE_D                        | PHASE_D                          |                    |

| M_CLK:0          | BCLK                           | BCLK                             | W37                |

| S_CLK:3          |                                | RSVD_Y37                         | Y37                |

| S_CLK:2          |                                | TDI                              | AN35               |

| S_CLK:1          |                                | ТСК                              | AL33               |

| S_CLK:0          |                                | TMS                              | AK32               |

Table 2-1: Clock channels assignments

Table 2-2: Qualifier channel assignments

| Qualifier channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|-------------------|--------------------------------|----------------------------------|-------------------|

| M_QUAL:1          |                                | RSVD_X34                         | X34               |

| M_QUAL:0          |                                | RSVD_AF36                        | AF36              |

| S_QUAL:1          |                                | RSVD_X4                          | X4                |

| S_QUAL:0          |                                | TRST#                            | AN33              |

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| M_A3:7     | A31#                           | A31#                             | AD4               |

| M_A3:6     | A30#                           | A30#                             | AA3               |

| M_A3:5     | A29#                           | A29#                             | Z4                |

| M_A3:4     | A28#                           | A28#                             | AK6               |

| M_A3:3     | A27#                           | A27#                             | AA1               |

| M_A3:2     | A26#                           | A26#                             | Y3                |

| M_A3:1     | A25#                           | A25#                             | AF6               |

| M_A3:0     | A24#                           | A24#                             | AB4               |

| M_A2:7     | A23#                           | A23#                             | AB6               |

| M_A2:6     | A22#                           | A22#                             | AE3               |

| M_A2:5     | A21#                           | A21#                             | AJ1               |

| M_A2:4     | A20#                           | A20#                             | AC3               |

| M_A2:3     | A19#                           | A19#                             | AG3               |

| M_A2:2     | A18#                           | A18#                             | Z6                |

| M_A2:1     | A17#                           | A17#                             | AE1               |

| M_A2:0     | A16#                           | A16#                             | AN7               |

| M_A1:7     | A15#                           | A15#                             | AL5               |

| M_A1:6     | A14#                           | A14#                             | AK14              |

| M_A1:5     | A13#                           | A13#                             | AL7               |

| M_A1:4     | A12#                           | A12#                             | AN5               |

| M_A1:3     | A11#                           | A11#                             | AK10              |

| M_A1:2     | A10#                           | A10#                             | AH6               |

| M_A1:1     | A9#                            | A9#                              | AL9               |

| M_A1:0     | A8#                            | A8#                              | AH10              |

| M_A0:7     | A7#                            | A7#                              | AL15              |

| M_A0:6     | A6#                            | A6#                              | AN9               |

| M_A0:5     | A5#                            | A5#                              | AH8               |

| M_A0:4     | A4#                            | A4#                              | AH12              |

| M_A0:3     | A3#                            | A3#                              | AK8               |

Table 2-3: Master A channel assignments

| LA channel | IA32G5 support channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|-----------------------------|----------------------------------|-------------------|

| M_A0:2     | A2#                         | A2# <sup>§</sup>                 |                   |

| M_A0:1     | A1#                         | A1# <sup>§</sup>                 |                   |

| M_A0:0     | A0#                         | A0# <sup>§</sup>                 |                   |

Table 2-3: Master A channel assignments (cont.)

§ Forced to inactive state, except in MagniVu

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| M_D3:7     | ATTR7#                         | BNT_OBS#                         |                   |

| M_D3:6     | ATTR6#                         | SCNTE_D                          |                   |

| M_D3:5     | ATTR5#                         |                                  |                   |

| M_D3:4     | ATTR4#                         |                                  |                   |

| M_D3:3     | ATTR3#                         |                                  |                   |

| M_D3:2     | ATTR2#                         | SMI#                             | AJ35              |

| M_D3:1     | ATTR1#                         | IGNNE#                           | AG37              |

| M_D3:0     | ATTR0#                         |                                  |                   |

| M_D2:7     | DID7#                          | RSVD_L33                         | L33               |

| M_D2:6     | DID6#                          | FERR#                            | AC35              |

| M_D2:5     | DID5#                          | LINT1                            | L37               |

| M_D2:4     | DID4#                          | PICD1                            | L35               |

| M_D2:3     | DID3#                          | PICCLK                           | J33               |

| M_D2:2     | DID2#                          | BP2#                             | G33               |

| M_D2:1     | DID1#                          | BPM1#                            | E35               |

| M_D2:0     | DID0#                          | PRDY#                            | A35               |

| M_D1:7     | BE7#                           | AER_OBS#                         |                   |

| M_D1:6     | BE6#                           | RCNTE_D                          |                   |

| M_D1:5     | BE5#                           |                                  |                   |

| M_D1:4     | BE4#                           | STPCLK#                          | AG35              |

| M_D1:3     | BE3#                           | A20M#                            | AE33              |

| M_D1:2     | BE2#                           | RSVD_AN3                         | AN3               |

| M_D1:1     | BE1#                           | IERR#                            | AE35              |

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| M_D1:0     | BE0#                           | LINT0                            | M36               |

| M_D0:7     | EXF4#                          | PREQ#                            | J37               |

| M_D0:6     | EXF3#                          | RESERVED                         | R2                |

| M_D0:5     | EXF2#                          | RESERVED                         | N33               |

| M_D0:4     | EXF1#                          | BP3#                             | E37               |

| M_D0:3     | EXF0#                          | BPM0#                            | C35               |

| M_D0:2     |                                | A2_D# <sup>§</sup>               |                   |

| M_D0:1     |                                | A1_D# <sup>§</sup>               |                   |

| M_D0:0     |                                | A0_D# §                          |                   |

Table 2-4: Master D channel assignments (cont.)

§ Not valid in MagniVu

#### Table 2-5: Master C channel assignments

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| M_C3:7     | ADS#                           | ADS#                             | AN31              |

| M_C3:6     | DBSY#                          | DBSY#                            | AL27              |

| M_C3:5     | RPb#                           | BREQ0#                           | AN29              |

| M_C3:4     | HITM#                          | HITM#                            | AL23              |

| M_C3:3     | TRDY#                          | TRDY#                            | AN25              |

| M_C3:2     | AERR#                          | AERR#                            | AK24              |

| M_C3:1     | REQb4#                         | BPRI#                            | AN17              |

| M_C3:0     | REQb3#                         |                                  |                   |

| M_C2:7     | LOCK#                          | LOCK#                            | AK20              |

| M_C2:6     | REQb2#                         |                                  |                   |

| M_C2:5     | REQb0#                         |                                  |                   |

| M_C2:4     | REQb1#                         |                                  |                   |

| M_C2:3     | BNR#                           | BNR#                             | AH14              |

| M_C2:2     | APb0#                          |                                  |                   |

| M_C2:1     | APb1#                          |                                  |                   |

| M_C2:0     |                                |                                  |                   |

| M_C1:7     | RS2#                           | RS2#                             | AK28              |

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| M_C1:6     | DRDY#                          | DRDY#                            | AN27              |

| M_C1:5     | RP#                            | RP#                              | AN23              |

| M_C1:4     | HIT#                           | HIT#                             | AL25              |

| M_C1:3     | RS0#                           | RS0#                             | AH26              |

| M_C1:2     | RS1#                           | RS1#                             | AH22              |

| M_C1:1     | REQ4#                          | REQ4#                            | AL17              |

| M_C1:0     | REQ3#                          | REQ3#                            | AL19              |

| M_C0:7     | DEFER#                         | DEFER#                           | AN19              |

| M_C0:6     | REQ2#                          | REQ2#                            | AH18              |

| M_C0:5     | REQ0#                          | REQ0#                            | AK18              |

| M_C0:4     | REQ1#                          | REQ1#                            | AH16              |

| M_C0:3     | RSVD_AK30                      | RSVD_AK30                        | AK30              |

| M_C0:2     | AP0#                           | AP0#                             | AL11              |

| M_C0:1     | AP1#                           | AP1#                             | AN13              |

| M_C0:0     | RESET#                         | RESET#                           | AH4               |

Table 2-5: Master C channel assignments (cont.)

#### Table 2-6: Slave A channel assignments

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| S_A3:7     | D42#                           | D42#                             | D12               |

| S_A3:6     | D49#                           | D49#                             | C13               |

| S_A3:5     | D27#                           | D27#                             | F12               |

| S_A3:4     | D48#                           | D48#                             | A17               |

| S_A3:3     | D57#                           | D57#                             | A19               |

| S_A3:2     | D63#                           | D63#                             | F16               |

| S_A3:1     | D46#                           | D46#                             | A21               |

| S_A3:0     | D54#                           | D54#                             | C21               |

| S_A2:7     | D50#                           | D50#                             | C25               |

| S_A2:6     | D53#                           | D53#                             | A23               |

| S_A2:5     | D62#                           | D62#                             | E25               |

| S_A2:4     | DEP7#                          | DEP7#                            | A29               |

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| S_A2:3     | DEP6#                          | DEP6#                            | E29               |

| S_A2:2     | DEP4#                          | DEP4#                            | E31               |

| S_A2:1     | DEP0#                          | DEP0#                            | C33               |

| S_A2:0     | DEP3#                          | DEP3#                            | A31               |

| S_A1:7     | D45#                           | D45#                             | C11               |

| S_A1:6     | D51#                           | D51#                             | A13               |

| S_A1:5     | D40#                           | D40#                             | C15               |

| S_A1:4     | D47#                           | D47#                             | A15               |

| S_A1:3     | D59#                           | D59#                             | C17               |

| S_A1:2     | D41#                           | D41#                             | D14               |

| S_A1:1     | D52#                           | D52#                             | D16               |

| S_A1:0     | D55#                           | D55#                             | C19               |

| A_A0:7     | D58#                           | D58#                             | C23               |

| S_A0:6     | D60#                           | D60#                             | A25               |

| S_A0:5     | D61#                           | D61#                             | A27               |

| S_A0:4     | D56#                           | D56#                             | C27               |

| S_A0:3     | DEP5#                          | DEP5#                            | C29               |

| S_A0:2     | DEP1#                          | DEP1#                            | C31               |

| S_A0:1     | BINIT#                         | BINIT#                           | B36               |

| S_A0:0     | DEP2#                          | DEP2#                            | A33               |

Table 2-6: Slave A channel assignments (cont.)

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| S_D3:7     | D14#                           | D14#                             | N3                |

| S_D3:6     | D17#                           | D17#                             | R4                |

| S_D3:5     | D18#                           | D18#                             | P4                |

| S_D3:4     | D11#                           | D11#                             | M4                |

| S_D3:3     | D16#                           | D16#                             | H4                |

| S_D3:2     | D7#                            | D7#                              | J1                |

| S_D3:1     | D23#                           | D23#                             | G3                |

| S_D3:0     | D26#                           | D26#                             | E1                |

| S_D2:7     | D33#                           | D33#                             | C1                |

| S_D2:6     | D29#                           | D29#                             | A3                |

| S_D2:5     | D31#                           | D31#                             | C5                |

| S_D2:4     | D43#                           | D43#                             | A7                |

| S_D2:3     | D36#                           | D36#                             | C9                |

| S_D2:2     | D32#                           | D32#                             | F6                |

| S_D2:1     | D37#                           | D37#                             | A9                |

| S_D2:0     | D44#                           | D44#                             | A11               |

| S_D1:7     | D2#                            | D2#                              | N1                |

| S_D1:6     | D13#                           | D13#                             | L1                |

| S_D1:5     | D9#                            | D9#                              | P6                |

| S_D1:4     | D3#                            | D3#                              | M6                |

| S_D1:3     | D24#                           | D24#                             | K6                |

| S_D1:2     | D20#                           | D20#                             | L3                |

| S_D1:1     | D30#                           | D30#                             | J3                |

| S_D1:0     | D21#                           | D21#                             | G1                |

| S_D0:7     | D25#                           | D25#                             | E3                |

| S_D0:6     | D35#                           | D35#                             | B2                |

| S_D0:5     | D28#                           | D28#                             | A5                |

| S_D0:4     | D34#                           | D34#                             | C7                |

| S_D0:3     | D38#                           | D38#                             | D8                |

| S_D0:2     | D19#                           | D19#                             | H6                |

#### Table 2-7: Slave D channel assignments

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| S_D0:1     | D22#                           | D22#                             | F8                |

| S_D0:0     | D39#                           | D39#                             | D10               |

Table 2-7: Slave D channel assignments (cont.)

#### Table 2-8: Slave C channel assignments

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| S_C3:7     | Ab35#                          | RESERVED                         | X2                |

| S_C3:6     | Ab33#                          | PICD0                            | J35               |

| S_C3:5     | Ab32#                          | RSVD_AM2                         | AM2               |

| S_C3:4     | D0#                            | D0#                              | W1                |

| S_C3:3     | Ab34#                          | THRMTRP#                         | AH28              |

| S_C3:2     | SLP#                           | SLP#                             | AH30              |

| S_C3:1     | FLUSH#                         | FLUSH#                           | AE37              |

| S_C3:0     | RSVD_F10                       | RSVD_F10                         | F10               |

| S_C2:7     | BERR#                          | BERR#                            | V4                |

| S_C2:6     | D1#                            | D1#                              | T4                |

| S_C2:5     | D8#                            | D8#                              | S1                |

| S_C2:4     | D12#                           | D12#                             | Q1                |

| S_C2:3     | TRCK_ER_D                      | TRCK_ER_D                        |                   |

| S_C2:2     | RCNT1_D                        | RCNT1_D                          |                   |

| S_C2:1     | SCNT0_D                        | SCNT0_D                          |                   |

| S_C2:0     | SCNT2_D                        | SCNT2_D                          |                   |

| S_C1:7     | A35#                           | A35#                             | AF4               |

| S_C1:6     | A33#                           | A33#                             | AC1               |

| S_C1:5     | A32#                           | A32#                             | X6                |

| S_C1:4     |                                | PWRGOOD                          | AK26              |

| S_C1:3     | A34#                           | A34#                             | W3                |

| S_C1:2     | INIT#                          | INIT#                            | AG33              |

| S_C1:1     | RSP#                           | RSP#                             | AC37              |

| S_C1:0     | D4#                            | D4#                              | U1                |

| S_C0:7     | D15#                           | D15#                             | U3                |

TMSPGC PGA-370 SE/DIFF Clk Hardware Support

| LA channel | IA32G5 support<br>channel name | IA32G5_T support<br>channel name | CPU<br>pin number |

|------------|--------------------------------|----------------------------------|-------------------|

| S_C0:6     | D6#                            | D6#                              | T6                |

| S_C0:5     | D5#                            | D5#                              | S3                |

| S_C0:4     | D10#                           | D10#                             | Q3                |

| S_C0:3     | RCNT0_D                        | RCNT0_D                          |                   |

| S_C0:2     | RCNT2_D                        | RCNT2_D                          |                   |

| S_C0:1     | SCNT1_D                        | SCNT1_D                          |                   |

| S_C0:0     | SNOOP_D                        | SNOOP_D                          |                   |

Table 2-8: Slave C channel assignments (cont.)

# Specifications

# **Specifications**

This section contains information regarding the specifications of the TMSPGC PGA370 microprocessor hardware support.

# **Circuit Description**

|                | The following is a description of Signal Probing and JTAG circuitry.                                                                                                                                                                                                                                                   |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Probing | The TMSPGC probe adapter uses series isolation resistors on all signals. For most signals (see Figures 3-1 to 3-3), the probe adapter presents an active device load.                                                                                                                                                  |

| JTAG           | The TMSPGC probe adapter provides a connection point for JTAG debugging device. In addition to the JTAG (J490) port, the probe adapter contains circuitry to terminate the JTAG control and data signals to their appropriate voltage levels. The JTAG circuitry on the probe adapter supports only 1.5 V CMOS.        |

|                | When using the JTAG port on the probe adapter, a 363-pin protective socket must<br>be installed on the system under test to isolate the JTAG signals between the<br>system under test and the probe adapter. Isolating the JTAG signals allows the<br>probe adapter to control the JTAG signals on the microprocessor. |

|                | The JTAG circuitry on the probe adapter can only control the JTAG signals when<br>an JTAG device is plugged into the JTAG port on the logic board. When the<br>cable is removed, all JTAG data and control lines are tristated.                                                                                        |

|                | The 363-pin protective socket must be used only when an JTAG device is plugged into the JTAG port on the Logic board. When using the 363-pin protective socket, connect the JTAG device to the JTAG port on the Logic board, before powering on the system under test.                                                 |

## **Probe Adapter Loading Diagrams**

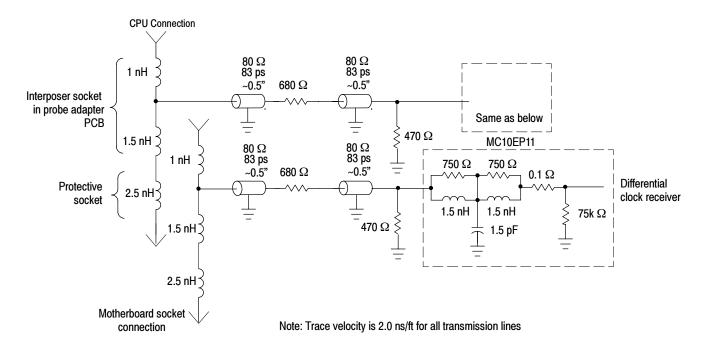

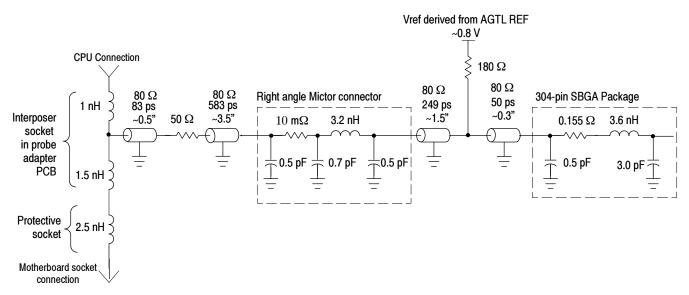

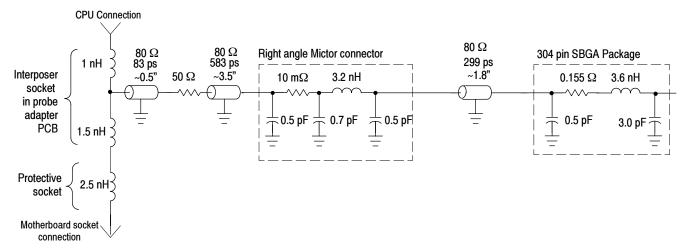

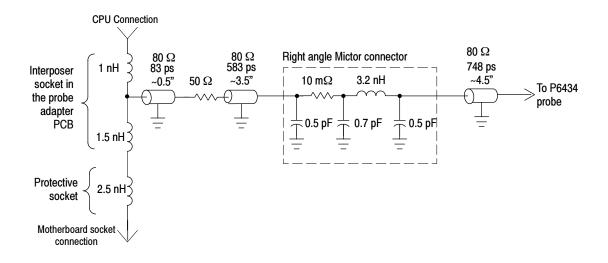

Figures 3-1 through 3-5 are provided for loading reference.

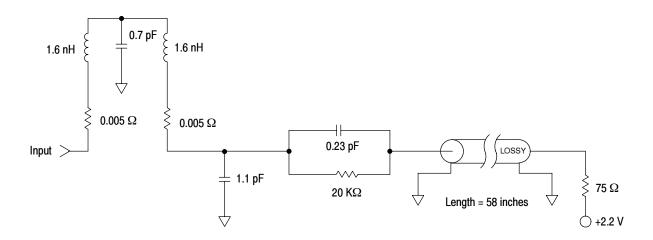

Figure 3-1: BCLK and BCLK# signals with active loads

Figure 3-2: AGTL signals with active loads, except RESET#

Figure 3-3: CMOS signals with active loads, plus RESET#

Figure 3-4: JTAG signals without active loads

Figure 3-5 applies only to those signals that do not have an active load.

#### Figure 3-5: Equivalent circuit for the P6434 probe

Table 3-1 shows the values you can use to calculate characteristics of the Lossy delay lines shown in Figure 3-5, which is the equivalent circuit of the P6434 probe.

Table 3-1: Lossy delay line values

| Characteristic             | Value                  |

|----------------------------|------------------------|

| C (capacitance)            | 1.58 pF per inch       |

| L (inductance)             | 8.9 nH per inch        |

| R (resistance)             | .067 $\Omega$ per inch |

| Z <sub>0</sub> (impedance) | 75 Ω                   |

## **Specification Tables**

These specifications are for the TMSPGC probe adapter connected between a Tektronix logic analyzer and a system under test.

Table 3-2 lists the electrical requirements of the system under test. Table 3-7 lists the electrical requirements for the AC adapter that provides power to the TMSPGC probe adapter. Table 3-8 lists the environmental specifications. Table 3-3 lists the BCLK timing restrictions and electrical specifications.

| Characteristics                          | Requirements |

|------------------------------------------|--------------|

| Maximum clock rate                       | 133 MHz      |

| Minimum setup time required, all signals | 1.0 ns       |

| Minimum hold time required, all signals  | 0.4 ns       |

#### Table 3-3: BCLK and BCLK# electrical specifications, differential clock

| Characteristics                | Minimum | Maximum | Units | Notes                    |

|--------------------------------|---------|---------|-------|--------------------------|

| V <sub>in</sub> (low)          | 0.1     | -       | V     |                          |

| V <sub>in</sub> (high)         | -       | 1.1     | V     |                          |

| Duty Cycle                     | 45      | 55      | %     |                          |

| t <sub>r</sub>                 | 0.3     | 0.6     | ns    | Monotonically increasing |

| t <sub>f</sub>                 | 0.3     | 0.6     | ns    | Monotonically decreasing |

| V <sub>in</sub> (differential) | ±0.3    | ± 1.0   | V     |                          |

| Characteristics        | Minimum     | Maximum     | Units | Notes                         |

|------------------------|-------------|-------------|-------|-------------------------------|

| V <sub>in</sub> (low)  | - 0.15      | CLKREF -0.3 | V     |                               |

| V <sub>in</sub> (high) | CLKREF +0.3 | 2.50        | V     |                               |

| Duty Cycle             | 45          | 55          | %     |                               |

| t <sub>r</sub>         | 0.3         | 0.6         | ns    | Monotonically increas-<br>ing |

| t <sub>f</sub>         | 0.3         | 0.6         | ns    | Monotonically de-<br>creasing |

| CLKREF                 | 1.17        | 1.33        | V     | 1.25 V 6.5%                   |

| Characteristics        | Minimum     | Maximum     | Units | Notes     |

|------------------------|-------------|-------------|-------|-----------|

| AGTL(1.2 V)            |             |             |       |           |

| V <sub>in</sub> (low)  | -0.15       | GTLREF -0.2 | V     |           |

| V <sub>in</sub> (high) | GTLREF +0.2 | 1.20        | V     |           |

| GTLREF                 | 0.776       | 0.824       | V     | 0.8 v ±3% |

| AGTLT(1.5 V)           |             |             |       |           |

| V <sub>in</sub> (low)  | -0.15       | GTLREF -0.2 | V     |           |

| V <sub>in</sub> (high) | GTLREF +0.2 | 1.50        | V     |           |

| GTLREF                 | 0.95        | 1.05        | V     | 1.0 v ±5% |

Table 3-5: AGTL electrical specifications

#### Table 3-6: CMOS electrical specifications (1.5 V)

| Characteristics        | Minimum      | Maximum      | Units | Notes      |

|------------------------|--------------|--------------|-------|------------|

| V <sub>in</sub> (low)  | -0.15        | CMOSREF -0.2 | V     |            |

| V <sub>in</sub> (high) | CMOSREF +0.2 | 1.50         | V     |            |

| CMOSREF                | 0.90         | 1.10         | V     | 1.0 v ±10% |

Table 3-7: Electrical specifications for the AC adapter

| Characteristic         | Description            |

|------------------------|------------------------|

| Input Voltage rating   | 100 - 250 VAC CAT II   |

| Input Frequency Rating | 47 - 63 Hz             |

| Input Current Rating   | 1 A Maximum, at 90 VAC |

| Output Voltage Rating  | 5 V                    |

| Output Current Rating  | 8 A                    |

| Output Power Rating    | 40 W                   |

| Characteristic <sup>1</sup> | Description                                |  |  |

|-----------------------------|--------------------------------------------|--|--|

| Temperature                 |                                            |  |  |

| Maximum operating           | +50 °C (+122° F) <sup>2</sup>              |  |  |

| Minimum operating           | 0 °C (+32 °F)                              |  |  |

| Nonoperating                | -55 °C to +75 °C (-67 ° to +167 °F)        |  |  |

| Humidity                    | 10 to 95% relative humidity, noncondensing |  |  |

| Altitude                    |                                            |  |  |

| Operating                   | 4.5 km (15,000 ft) maximum                 |  |  |

| Nonoperating                | 15 km (50,000 ft) maximum                  |  |  |

| Electrostatic immunity      | The probe adapter is static sensitive      |  |  |

#### Table 3-8: Environmental specifications

<sup>1</sup> Designed to meet Tektronix standard 062-2847-00 class 5.

<sup>2</sup> Not to exceed microprocessor thermal considerations. Forced air cooling may be required across the CPU.

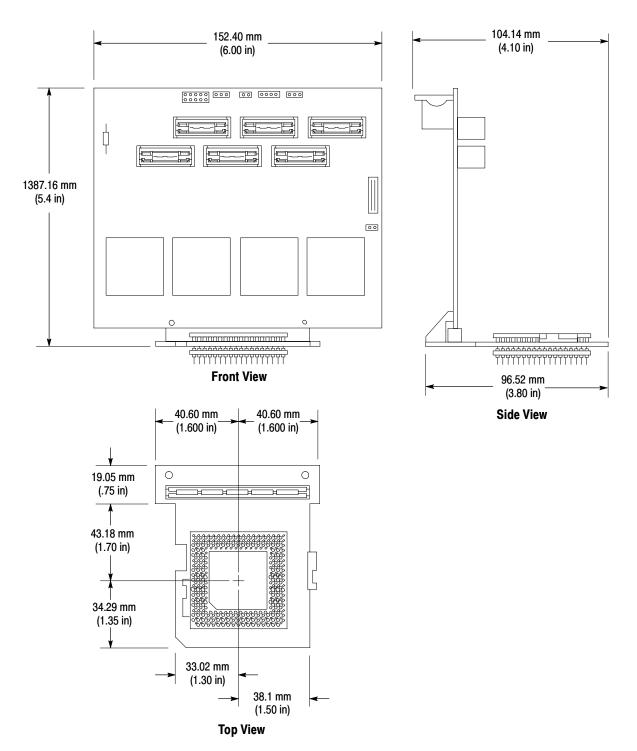

**Dimensions** Figure 3-6 shows the dimensions of the TMSPGC probe adapter.

Figure 3-6: Dimensions of the TMSPGC probe adapter

# Maintenance

# Maintenance

This section contains information on replacing the probe-adapter fuse.

### **Replacing The Fuse**

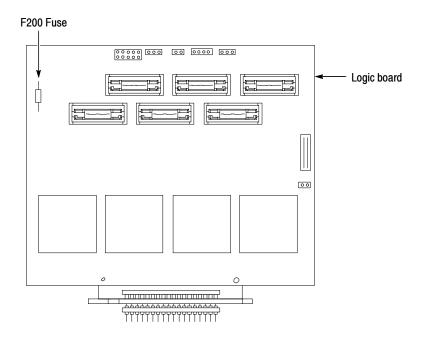

If the fuse on the probe adapter opens (burns out), you can replace it with a 7 A, 125 V fuse. Figures 4-1 illustrates the location of the fuse on the TMSPGC probe adapter. See the *Replaceable Mechanical Parts* chapter for part descriptions.

Figure 4-1: Fuse location on the TMSPGC probe adapter

Maintence

# **Replaceable Parts List**

# **Replaceable Parts List**

This section contains a list of the replaceable components for the TMSPGC PGA370 Hardware support package.

#### **Parts Ordering Information**

Replacement parts are available through your local Tektronix field office or representative.

Changes to Tektronix products are sometimes made to accommodate improved components as they become available and to give you the benefit of the latest improvements. Therefore, when ordering parts, it is important to include the following information in your order:

- Part number

- Instrument type or model number

- Instrument serial number

- Instrument modification number, if applicable

If you order a part that has been replaced with a different or improved part, your local Tektronix field office or representative will contact you concerning any change in part number.

#### **Using the Replaceable Parts List**

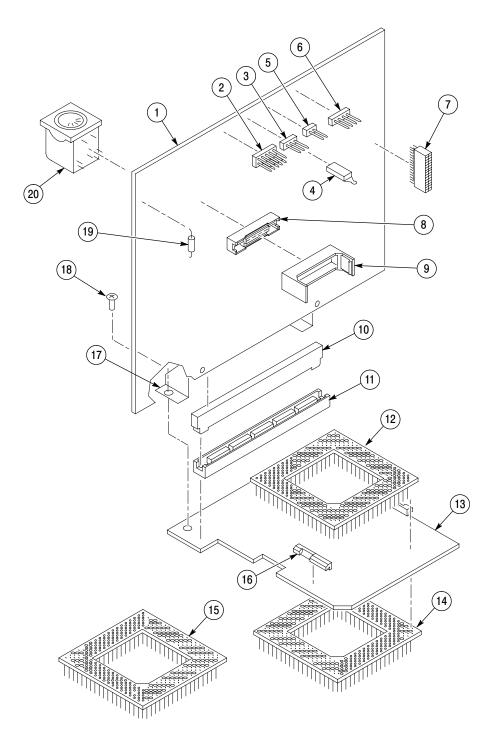

The tabular information in the Replaceable Parts List is arranged for quick retrieval. Understanding the structure and features of the list will help you find all of the information you need for ordering replacement parts. The following table describes the content of each column in the parts list.

#### Parts list column descriptions

| Column  | Column name           | Description                                                                                                                                                                                                                    |

|---------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Figure & index number | Items in this section are referenced by figure and index numbers to the exploded view illustrations that follow.                                                                                                               |

| 2       | Tektronix part number | Use this part number when ordering replacement parts from Tektronix.                                                                                                                                                           |

| 3 and 4 | Serial number         | Column three indicates the serial number at which the part was first effective. Column four indicates the serial number at which the part was discontinued. No entries indicates the part is good for all serial numbers.      |

| 5       | Qty                   | This indicates the quantity of parts used.                                                                                                                                                                                     |

| 6       | Name & description    | An item name is separated from the description by a colon (:). Because of space limitations, an item name may sometimes appear as incomplete. Use the U.S. Federal Catalog handbook H6-1 for further item name identification. |

| 7       | Mfr. code             | This indicates the code of the actual manufacturer of the part.                                                                                                                                                                |

| 8       | Mfr. part number      | This indicates the actual manufacturer's or vendor's part number.                                                                                                                                                              |

Abbreviations Abbreviations conform to American National Standard ANSI Y1.1-1972.

# **Chassis Parts** Chassis-mounted parts and cable assemblies are located at the end of the Replaceable Electrical Parts List.

#### Mfr. Code to Manufacturer Cross Index

The table titled Manufacturers Cross Index shows codes, names, and addresses of manufacturers or vendors of components listed in the parts list.

#### Manufacturers cross index

| Mfr.   |                              |                                                       |                            |

|--------|------------------------------|-------------------------------------------------------|----------------------------|

| code   | Manufacturer                 | Address                                               | City, state, zip code      |

| 80009  | TEKTRONIX INC                | 14150 SW KARL BRAUN DR<br>PO BOX 500                  | BEAVERTON, OR 97077-0001   |

| 14310  | AULT INC                     | 7105 NORTHLAND TERRACE                                | MINNEAPOLIS, MN 55428-1534 |

| 3N087  | MILL-MAX MANUFACTURING CORP  | 190 PINE HOLLOW RD<br>PO BOX 300                      | OYSTER BAY, NY 11771       |

| 46384  | PENN ENGINEERING & MFG CORP  | OLD EASTON RD<br>PO BOX 1000                          | DANBORO, PA 18916          |

| 5Y400  | TRIAX METAL PRODUCTS INC     | 1880 SW MERLO DRIVE                                   | BEAVERTON, OR 97006        |

| TK0AT  | AMP, INC                     | 7-15-14 ROPPONGI<br>MINATO-KU                         | TOKYO JAPAN,               |

| TK2548 | XEROX CORPORATION            | 14181 SW MILLIKAN WAY                                 | BEAVERTON, OR 97005        |

| 00779  | TYCO ELECTRONICS CORPORATION | CUSTOMER SERVICE DEPT<br>PO BOX 3608                  | HARRISBURG, PA 17105-3608  |

| 07707  | POP FASTENERS                | 510 RIVER RD                                          | SHELTON, CT 06484-4517     |

| 26742  | METHODE ELECTRONICS INC      | 7444 WEST WILSON AVE                                  | CHICAGO, IL 60656-4548     |

| 50579  | SIEMENS COMPONENTS INC       | OPTOELECTRONICS DIVISION<br>1900 HOMESTEAD RD         | CUPERTINO, CA 95014        |

| 53387  | 3M COMPANY                   | ELECTRONICS PRODUCTS DIV<br>3M AUSTIN CENTER          | AUSTIN, TX 78769-2963      |

| 59124  | KOA SPEER ELECTRONICS INC    | BOLIVAR DRIVE<br>PO BOX 547                           | BRADFORD, PA 16701         |

| 60381  | PRECISION INTERCONNECT CORP. | 16640 SW 72ND AVE                                     | PORTLAND, OR 97224         |

| 61429  | FOX ELECTRONICS              | DIV OF FOX ENTERPRIXED INC<br>5842 CORPORATION CIRCLE | FORT MEYERS, FL 33905      |

| 61857  | SAN-O INDUSTRIAL CORP        | 91-3 COLIN DRIVE                                      | HOLBROOK, NY 11741         |

#### Replaceable parts list

| Fig. &<br>index | Tektronix part           | Serial no. | Serial no. |     |                                                                                                        | Mfr.   |                           |

|-----------------|--------------------------|------------|------------|-----|--------------------------------------------------------------------------------------------------------|--------|---------------------------|

| number          | number                   | effective  | discont'd  | Qty | Name & description                                                                                     | code   | Mfr. part number          |

| 5-1-0           | 010-0643-00 <sup>†</sup> |            |            | 1   | PROBE ADAPTER:PGA-370,BASE AND LOGIC<br>BOARDS,TMSPGC                                                  | 80009  | 010-0643-00               |

| 1               | 671-5298-00              |            |            | 1   | CIRCUIT BOARD:LOGIC,TMSPGC,                                                                            | 80009  | 671-5298-00               |

| 2               | 131-5267-00              |            |            | 1   | CONN,HDR:PCB,MALE,STR,2 X 40,0.1 CTR,0.235 MLG X 0.110 TAIL,30GOLD, HIGH TEMP,                         | 00779  | 104326-4                  |

| 3               | 131-4530-00              |            |            | 2   | CONN,HDR:PCB,MALE,STR,1 X 3,0.1 CTR,0.230 MLG X 0.120<br>TAIL,30 GOLD,BD RETENTION,                    | 00779  | 104344-1                  |

| 4               | 131-4356-00              |            |            | 2   | CONN,SHUNT:SHUNT/SHORTING,FEMALE,1X2,0.1CTR,0.63<br>H,BLK,W/HANDLE,JUMPER,30 GOLD,                     | 26742  | 9618-302-50               |

| 5               | 131-4917-00              |            |            | 2   | CONN,HDR:PCB,MALE,STR,1 X 2,0.1 CTR,0.235 MLG X 0.110<br>TAIL,30 GOLD,TUBE,HIGH TEMP,                  | 00779  | 104350-1                  |

| 6               | 131-2919-01              |            |            | 1   | CONN,HDR:PCB,MALE,STR,1 X 4,0.1 CTR,0.235 MLG X 0.112<br>TAIL,30 GOLD,0.035 DIA PCB,SAFETY             | 53387  | 2404-6112TB               |

| 7               | 131-6023-00              |            |            | 1   | CONN,BOX:PCB,FEMALE,STR,2 X 15,0.05 X 0.1 CTR,0.350 H<br>X 0.1 TAIL,30 GOLD,SYS 50,                    | 00779  | 104078-4                  |

| 8               | 131-6134-01              |            |            | 6   | CONN,RCPT:SMD,MICTOR,FEMALE,STR,38 POS,0.025<br>CTR,0.240 H,W/0.108 PCB HOLD DOWNS.PALLADIUM           | 00779  | 767054-1                  |

| 9               | 105-1089-00              |            |            | 6   | LATCH ASSY:LATCH HOUSING ASSY,VERTICAL MOUNT,0.48<br>H X 1.24 L,W/PCB SINGLE CLIP,P6434                | 60381  | 105-1089-00               |

| 10              | 131-6465-00              |            |            | 1   | CONN,PLUG:SMD/EDGE MOUNT,MICTOR,MALE,RTANG,190<br>POS,0.025 CTR,0.209 H,PALLADIUM NICKEL,MATC          | TK0AT  | 767039-5                  |

| 11              | 131-6466-00              |            |            | 1   | CONN,RCPT:SMD,MICTOR,FEMALE,STR,190 POS,0.025<br>CTR,0.240 H,PALLADIUM NICKEL,IMPEDANCE MATCH          | TK0AT  | 767054-5                  |